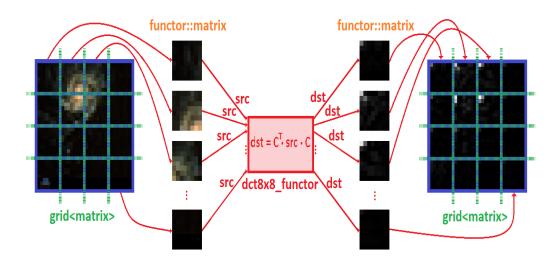

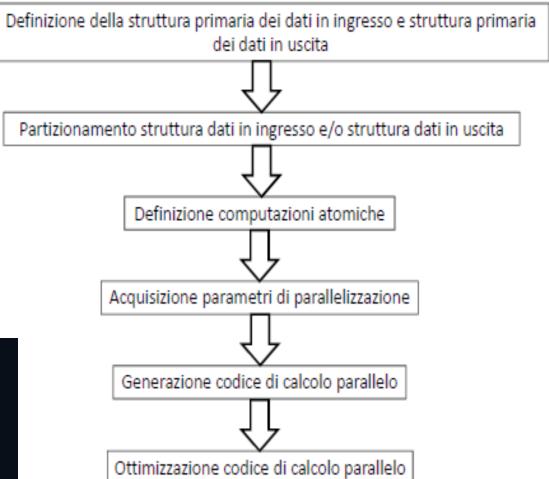

## Process for the automatic generation of parallel code

**INVENTORS:** Sandro Bartolini Biagio Peccerillo

**PATENT STATUS:** filed

**PRIORITY NUMBER:** 102017000082213

**PUBLICATION: -**

Invention

The present invention aims to solve the problems related to multi-architecture parallel programming. This uses an innovative and automatic process for the generation of parallel code with a high level of abstraction executable at high performance on electronic processors with heterogeneous multi-core or many-core or hybrid architectures. This code is automatically generated starting from code developed according to the structures typically used for sequential writing. The use of this procedure considerably reduces objective metrics generally adopted for measuring the complexity of programs and the effort to write them. Finally, the procedure allows you to optimize the parallel code generated based on the architecture of the target computer, without altering the source but by intervening on parameters orthogonal to the application code. The most significant advantages include: the facilitation of the programmer's task, since the parallel code is generated automatically; the considerable reduction of the objective metrics generally adopted to measure the complexity of programs and the effort to write them, such as lines of code, Halstead's mental discriminations and McCabe's total cyclomatic complexity; its easy applicability even on machines with different architectures; the decoupling of application semantics from high-performance parallel coding of code that is executed by a multi-core or many-core architecture; the adjustment of parallelization parameters that allows to optimize performance without altering the code written by the programmer.

Drawings & pictures

## Industrial applications

The technology can be applied in various fields, such as Industry 4.0 and specifically in automotive (autonomous driving), ICT and photonics, computer-vision, big-data processing, modeling of physical phenomena (mechanical, meteorological, fluid-dynamics), advanced graphics, multimedia content processing, apps, smart factory (robotic solutions) and videogames.

Possible developments

The research group is open to further technological development projects in any sector of application, which is of interest to companies operating in the same areas. In this regard, the University of Siena is available to sign specific development, license or option agreements for the direct enhancement of the patent title in question. The University of Siena is available to negotiate specific agreements for the technological maturation, license or option of the patent title linked to the invention.

For more information:

Tech Transfer Office of the Università degli Studi di Siena

Headquarters: via Banchi di Sotto 55, 53100 Siena ITALIA

website: https://www.unisi.it/

E-mail: brevetti@unisi.it

For more information:

Ufficio Regionale di Trasferimento Tecnologico

Headquarters: Via Luigi Carlo Farini, 8 50121 Firenze (FI)

E-mail: urtt@regione.toscana.it